基于ISO/IEC 14443-A协议的无源电子标签数字集成电路设计

随着物联网(IoT)和自动识别技术的飞速发展,非接触式智能卡与电子标签在门禁、支付、物流追踪等领域得到了广泛应用。其中,基于ISO/IEC 14443-A协议的无源电子标签,因其无需内置电源、通过射频场获取能量并通信的特点,成为了低成本、高可靠性的关键解决方案。其核心——数字集成电路(IC)的设计,直接决定了标签的性能、功耗、安全性与成本。本文将系统阐述基于14443-A协议的无源电子标签数字集成电路的设计要点与流程。

一、 系统架构与协议概述

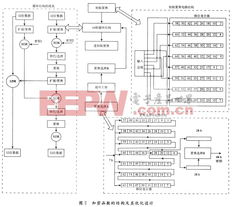

无源电子标签,或称射频识别(RFID)标签,其数字集成电路是标签的“大脑”。它必须完整实现ISO/IEC 14443-A协议栈的物理层与部分数据链路层功能。一个典型的数字IC架构主要包括:

- 数字基带处理器:这是设计的核心,负责协议时序控制、命令解析、响应生成、防冲突算法(如ISO 14443-3定义的比特级防冲突与寻址)以及与应用数据的交互。

- 存储控制器与存储器:管理标签内部的非易失性存储器(通常为EEPROM或新型低功耗存储器),用于存储唯一的标识符(UID)、用户数据以及安全密钥等。

- 安全与加密模块(可选但日益重要):实现如CRYPTO1(MIFARE Classic)或更高级的AES等加密算法,以保障数据传输的安全性,防止克隆与窃听。

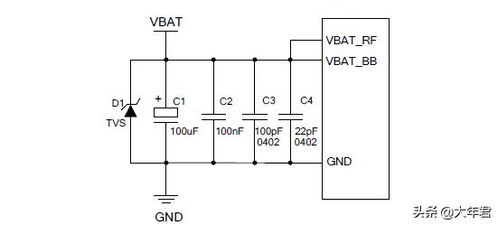

- 时钟管理与复位电路:从载波中恢复并分频产生系统所需的时钟,管理上电复位、掉电检测等关键状态。

- 模拟前端接口:与模拟部分(解调器、负载调制器等)的接口逻辑,负责将解调出的曼彻斯特编码或改进米勒编码的数字信号进行采样恢复,并控制负载调制器以NRZ或曼彻斯特编码格式返回数据。

二、 关键设计考量与挑战

- 超低功耗设计:由于标签能量完全来自读写器发射的射频场,功耗是设计的首要约束。设计中需采用:

- 门控时钟技术:对非活动模块动态关闭时钟,大幅降低动态功耗。

- 多阈值电压设计:对非关键路径使用高阈值电压晶体管以降低静态漏电。

- 全静态逻辑与异步设计:在允许的模块中避免使用动态逻辑,甚至采用异步电路设计,进一步消除时钟树功耗。

- 精细的电源管理:设计多级唤醒与休眠模式,使芯片在空闲时处于极低功耗状态。

- 协议兼容性与稳健性:数字基带处理器必须精确符合14443-A的时序要求(如帧延迟时间FDT),并能鲁棒地处理来自读写器的命令帧(帧格式、CRC校验等)。抗干扰能力和误码恢复机制也至关重要。

- 面积与成本优化:标签IC是典型的成本敏感型产品。设计需通过架构优化、逻辑综合与物理设计的精心规划,最小化芯片面积。复用逻辑模块、采用紧凑的存储器IP以及简化状态机都是常用手段。

- 安全性设计:对于高安全应用,需集成真随机数发生器(TRNG)、加密协处理器和防侧信道攻击(如功耗分析、时序分析)的防护电路。这增加了设计的复杂度与验证难度。

三、 典型设计流程

- 规范与架构定义:深入理解14443-A协议标准,明确功能、性能、功耗和面积目标,定义顶层架构和模块划分。

- RTL设计与功能验证:使用硬件描述语言(如Verilog/VHDL)进行寄存器传输级设计。搭建测试平台进行详尽的功能仿真,确保协议兼容性和逻辑正确性。功耗估算也在这一阶段开始进行。

- 逻辑综合与可测性设计:使用目标工艺库将RTL代码综合为门级网表,插入扫描链等可测性设计(DFT)结构,以便后续生产测试。

- 物理设计与验证:进行布局布线,完成时钟树综合、电源规划、时序收敛和信号完整性分析。这是实现超低功耗和面积优化的关键阶段。

- 后仿真与流片:提取寄生参数进行带时序信息的后仿真,最终生成GDSII文件交付晶圆厂流片。

- 测试与认证:芯片返回后,进行严格的实验室测试和场测,确保其功能、性能、功耗及与标准读写器的互操作性,最终通过相关认证(如NFC Forum认证)。

四、 发展趋势

未来的设计趋势将聚焦于:

- 更先进的工艺节点:向55nm、40nm甚至更小节点迁移,以进一步降低功耗和成本。

- 增强集成度:集成传感器接口(温度、湿度等),向“智能传感标签”演进。

- 更高的安全性:集成国密算法或更强大的安全内核,满足物联网安全需求。

- 能量收集增强:优化电路以在更弱的射频场中工作,扩大读写距离。

结论

基于ISO/IEC 14443-A协议的无源电子标签数字集成电路设计,是一项融合了通信协议、超低功耗数字设计、模拟混合信号接口和半导体工艺的综合性工程。成功的核心在于在严格的功耗和成本约束下,实现协议要求的全部功能,并保证高度的可靠性与稳健性。随着技术的不断演进,此类芯片将在万物互联的智能世界中扮演愈加重要的角色。

如若转载,请注明出处:http://www.jisuyijian.com/product/62.html

更新时间:2026-04-18 01:18:38